经过近三十年的发展,半导体芯片制造商现在可以使用新一代ASML的集成电路制造工具。新的生产线采用了最先进的极紫外(EUV)光刻工艺,该工艺使用波长为13.5 nm的光,从而使未来创新型CPU芯片的硅构建块尺寸减小了几纳米。

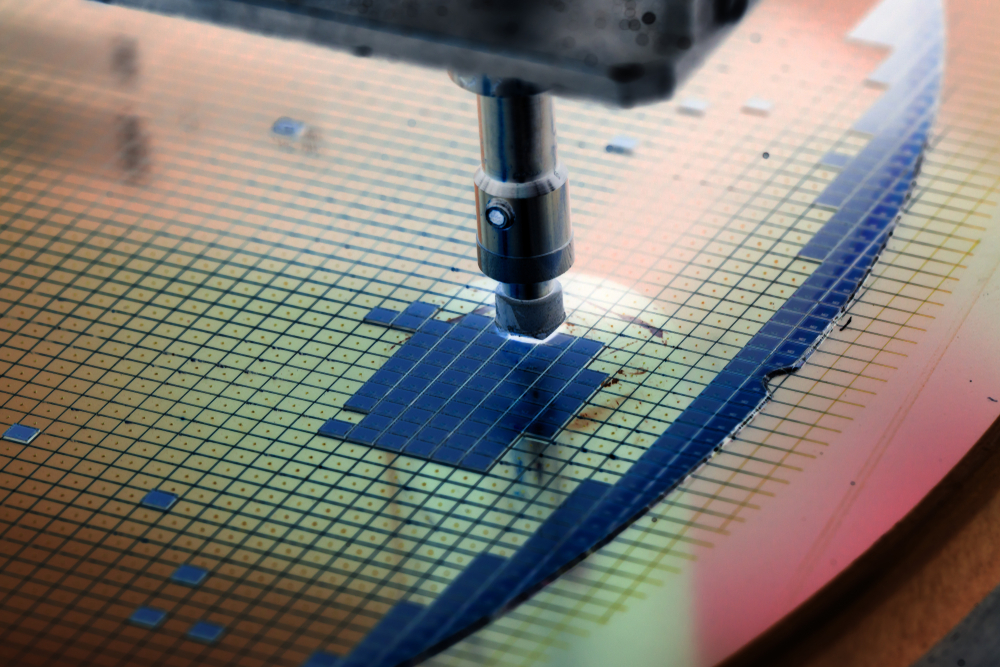

到目前为止,芯片制造商已采用光刻工艺,该工艺使用紫外(UV)光将复杂的图案投射到涂有光敏聚合物(称为光致抗蚀剂)的硅片上。该过程类似于旧纸质照片的显影。用金属显影,蚀刻或涂覆照明图案,以隔离或传导集成电路结构的一层内的结构。此过程可以逐层重复数百次,直到完成形成集成电路(例如微处理器)的晶体管的复杂互连网络为止。

密集封装集成电路设计

对计算能力和数据存储容量的不断增长的需求,以及对降低成本和功耗的需求,驱使计算机芯片制造商追求更先进,更高效的集成电路设计。

在过去的五十年中,新一代计算机芯片的开发遵循着一条简单的规则,即摩尔定律,该定律指出,密集封装的集成电路中的元素数量大约每两年翻一番。

空间分辨率障碍

在现代硅芯片中,晶体管尺寸不断缩小的一个重大限制来自光学定律。在19的端个世纪,德国物理学家恩斯特阿贝发现,在光学显微镜(样品的两个特征之间的最小可分辨的距离)的分辨率正比于用于样品照射的光的波长(λ)与显微镜透镜和样品之间的介质的折射率成反比。

相同的原理对于任何基于光的投影系统(包括光刻半导体制造工具)均有效。这就是为什么在光刻工艺中使用的光的波长起关键作用的原因。

波长较短,晶体管较小

结果,科学家和工程师一直在寻找波长越来越短的光源,以在半导体芯片中产生更小的特征。从紫外线汞蒸汽灯开始,到1970年代中期晶体管尺寸降至1 µm以下时,他们转向了强大的氟化氩(ArF)准分子激光器,产生波长为λ= 193 nm的深紫外线(DUV)光,之后又在波长λ = 157nm。

这些发展使芯片制造商在过去的几十年中通过将芯片的逻辑元件特征缩小到130 nm,然后是65 nm,最后是20 nm以下,大大提高了半导体芯片中的晶体管密度。这有助于以降低的成本生产更快,更高效的集成电路。

历史上,以纳米为单位的度量是指给定的光刻工艺可以产生的晶体管栅极的最小实际尺寸。这些数字已成为名义数字,表明芯片制造商正在使用的不同制造工艺,被称为技术节点。

不断增长的大量生产的集成电路目前正在从10 nm边界向7 nm及其以下的技术节点发展。

具有下一代5G连接能力的移动计算,人工智能,自动驾驶和高性能计算等众多应用将受益于下一代创新CPU芯片可提供的更高性能和能效。

半导体行业的下一代光刻系统

为了满足需求,三个主要的半导体制造商,台积电(台湾半导体制造公司),英特尔和三星,已经采用了TWINSCAN NXE:3400C EUV光刻扫描仪,最新和最先进的ASML半导体制造工具,以及唯一可商购的EUV光刻系统。

TWINSCAN NXE:3400C具有十万多个组件,是有史以来最复杂的机器之一。它的EUV光源由功能最强大的批量生产的激光系统泵浦。该机器重180吨,总共消耗1兆瓦以上的电力,成本为1.2亿美元。

EUV工业光源

机器的核心是由Zeiss SMT(总部位于德国Oberkochen的卡尔·蔡司半导体制造技术公司和ASML的长期合作伙伴)开发的EUV光学系统。EUV辐射表示波长在124 nm至10 nm之间的软X射线。恒星在其日冕的过热等离子体中产生EUV光。

蔡司的科学家和工程师开发了一种独特的光源,恰当地命名为Starlith®,它可以产生激光脉冲等离子体(LPP),该激光脉冲等离子体发射出λ= 13.5 nm的EUV光。光源由每秒脉冲50,000次的40 kW CO 2激光泵浦(由位于迪琴根的德国Trumpf公司制造)。每个激光脉冲都会立即蒸发出一小滴熔融锡(直径10-20 µm),该锡滴变成过热的EUV发射等离子体。

EUV光刻技术可制造创新的CPU芯片

NXE:3400C中的EUV光学器件是从头开始设计的,并且完全基于镜面(因为没有对EUV透明的材料)。锡等离子体的等离子体辐射由一个巨大的非球面反射镜收集,该反射镜在13.5 nm处的平均反射率约为40%。一组超精密反射镜进一步使来自收集器反射镜的EUV光束成形。它照亮了标线片(或光掩模),其中包含要转移到硅晶圆表面的复杂图案。第二组超平镜将来自掩模版的图案化EUV光束投射到晶圆表面上,向晶圆表面传递了250 W的功率,每小时曝光170枚晶圆的产量,空间分辨率为只有13纳米。

EUV光刻工艺的改进的空间分辨率大大降低了芯片制造工艺的复杂性,并提高了设计灵活性,缩短了制造时间,降低了成本,并为最终产品提供了出色的电路性能。

由于采用了ASML的NXE:3400C EUV光刻扫描仪,台积电已经在其5nm工艺节点上推出了其商用芯片,包括用于旗舰iPhone 12的苹果最新的A14处理器。其他芯片制造商将紧随其后的是创新的CPU芯片,先进的内存以及用于5G连接的高效节能集成电路。

EUV之后会发生什么?

ASML和Zeiss SMT的工程师已经在预料到未来的发展,这些发展可能使芯片制造商可以将更多的逻辑元件和存储器封装到他们的半导体器件中。

为了满足更高光刻分辨率的需求,ASML和Zeiss SMT正在开发高数值孔径EUV(或高NA EUV)扫描仪(宣布为NXE Next)。光学系统的数值孔径是衡量光学系统可以将多少光传递到样品表面的度量,并且是决定系统空间分辨率的一个因素。当前的EUV光学系统的NA值为0.33。下一代EUV扫描仪的NA值为0.55,空间分辨率小于8 nm。

参考资料:

ASML (2020) TWINSCAN NXE:3400C. [Online] www.asml.com Available at: https://www.asml.com/en/products/euv-lithography-systems/twinscan-nxe3400c (Accessed on 27 October 2020).

A. Shilov (2020) ASML Ramps Up EUV Scanners Production: 35 in 2020, Up to 50 in 2021. [Online] www.anandtech.com Available at: https://www.anandtech.com/show/15428/asml-ramps-up-euv-scanners-production-35-in-2020-45-50-in-2021 (Accessed on 27 October 2020).

M. Lapedus (2020) EUV’s Uncertain Future At 3nm And Below. [Online] www.semiengineering.com Available at: https://semiengineering.com/whats-next-for-euv (Accessed on 27 October 2020).

D. Rotman (2020), We’re not prepared for the end of Moore’s Law. [Online] www.technologyreview.com Available at: https://www.technologyreview.com/2020/02/24/905789/were-not-prepared-for-the-end-of-moores-law (Accessed on 27 October 2020).

M. Van de Kerkhof et al., (2020). High-power EUV lithography: spectral purity and imaging performance. J. of Micro/Nanolithography, MEMS, and MOEMS, 19(3), 033801. Available at: https://doi.org/10.1117/1.JMM.19.3.033801

文章原作者:Cvetelin Vasilev,

网站来源:https://www.azonano.com/article.aspx?ArticleID=5583

如果您对上述技术有兴趣的话,欢迎与我沟通交流。 如果您想了解更多光刻及光刻胶知识库,欢迎关注Litho+wiki,获取更多信息……

Views: 445

Leave A Comment?